diezclos11

Newbie

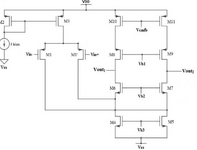

I am currently designing common-mode feedback for a fully differentially folded cascode with pmos inputs. As the operation of my folded cascode has a reset phase, I am only using two capacitors for my cmfb, as shown in the figure attached. When choosing the value for the capacitor,, I have a few doubts. For one side, it will load the output of the amplifier, requiring then a lower value for your caps. On the other hand, you would also want these capacitors to be considerably bigger than the parasitics of the gate of the current source (where the cmfb will be applied). Additionally, the SC-CMFB will introduce KT/C noise. So my question is the following:

- As the kt/c noise will be applied to the gate of both common sources, these noise will be seen as common mode noise, therefore rejected. However, this would require perfectly matched transistors (which is certainly not the case). Is there a way to annalitically determine which will be then the input referred noise contribution of the SC-CMFB (maybe considering the % of missmatch and then deriving the noise as you would normally do from the gate of these current sources)?

Any help would be really appreciated.

- As the kt/c noise will be applied to the gate of both common sources, these noise will be seen as common mode noise, therefore rejected. However, this would require perfectly matched transistors (which is certainly not the case). Is there a way to annalitically determine which will be then the input referred noise contribution of the SC-CMFB (maybe considering the % of missmatch and then deriving the noise as you would normally do from the gate of these current sources)?

Any help would be really appreciated.