shuy

Newbie level 4

hi all,

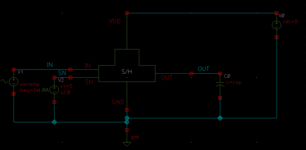

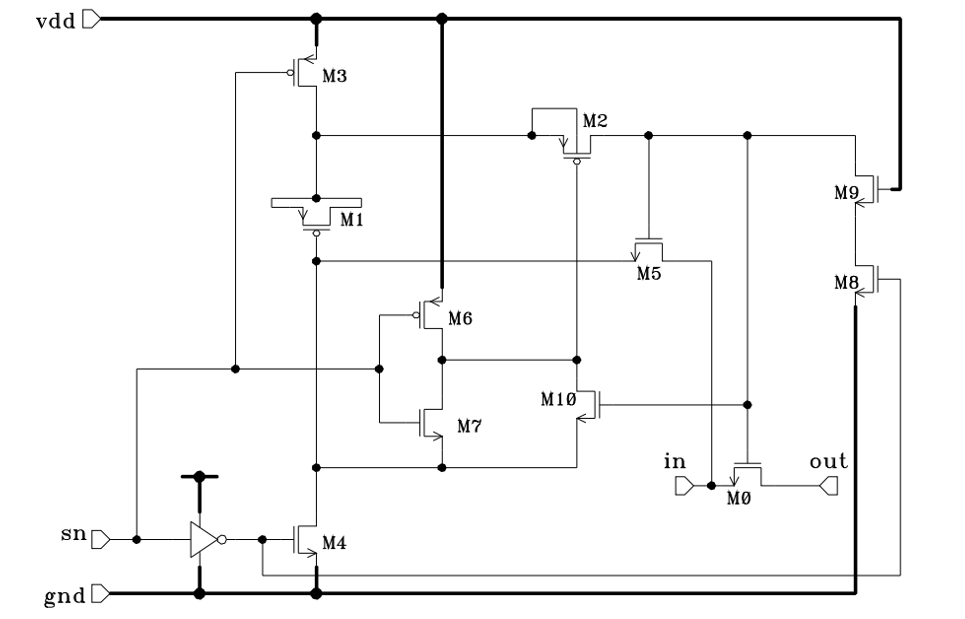

As part of the ADC design project, I designed a switch based on bootstrapping technique. I would appreciate help regarding the function of the transistor M10. It seems to work in parallel with M7 so it can be omitted.

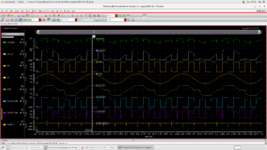

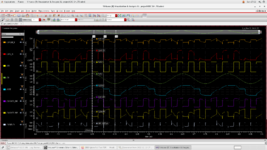

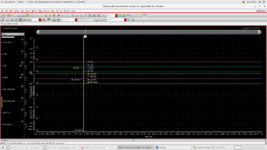

After simulations in Virtuoso, I saw that the circuit functions even better without it.

Thank you

As part of the ADC design project, I designed a switch based on bootstrapping technique. I would appreciate help regarding the function of the transistor M10. It seems to work in parallel with M7 so it can be omitted.

After simulations in Virtuoso, I saw that the circuit functions even better without it.

Thank you