prcken

Advanced Member level 1

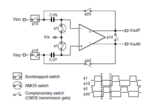

please have a look at this SH schematic, the wired thing is that I have to connect vcm at phase 1a to the differential input to make it operational. in theory it should work without that Vcm to inputs at 1a phase, for it is in feedback configuration at phase 2, the input common mode is set in the opamp itself with CMFB.

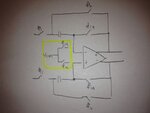

I checked some previous discussion in eadboard, even i tried with Seq switch in Razavi's book as below, it's still not functional.

because that Seq switch is intended for mitigate mismatch, here is seems not the mismatch problem. and seems not charge injection issue, either, because i tried to use ideal switches.

any ideas and comments ?

Thanks!