gagagagazi

Newbie

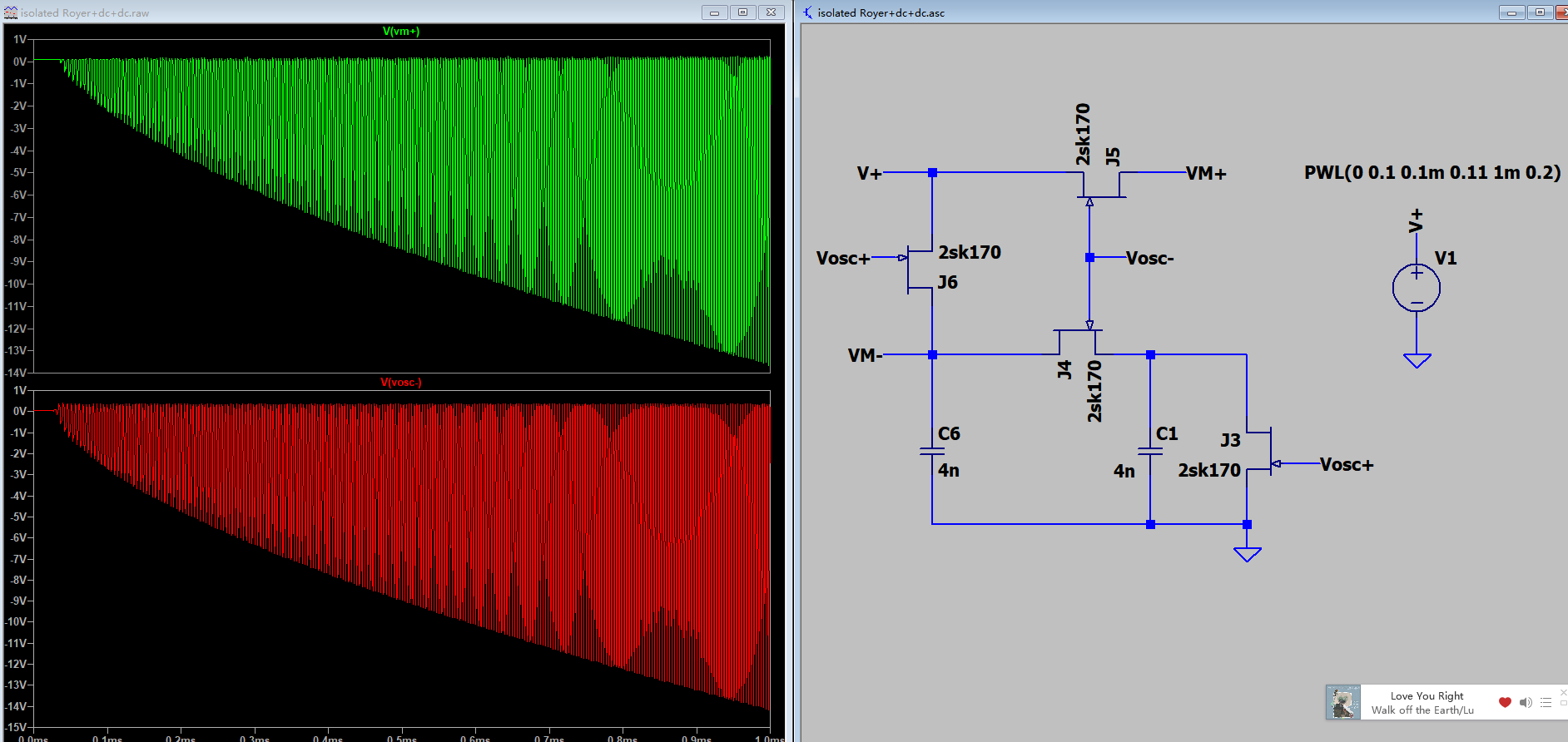

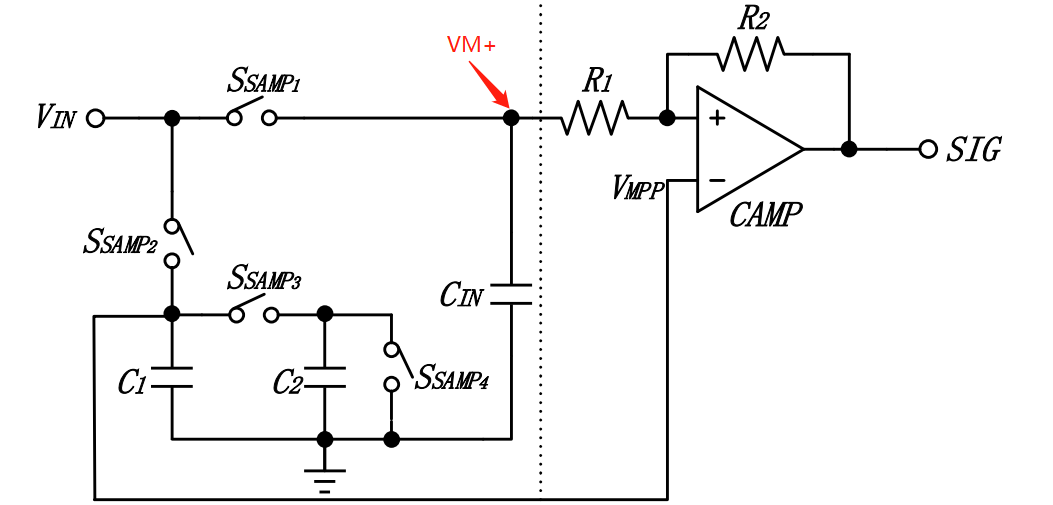

I am trying to study a Sample&Hold Citcuit, as shown in Fig.1, Vosc- and Vosc+ are the signals (opposite signals) that control J3~J6 generated by the pluse generator respectively, and the in Fig.2, my understanding It is when J4 and J5 are closed at the same time, the voltage of point VM+ should be the input voltage V+, but I don't know why, when I simulated in LTspice, the voltage of VM+ is almost the same as the signal Vosc- (as shown on the left side of Fig.1), I don't know what caused this, is there any solution? Thank you so much.

Fig.1

Fig.2

Fig.1

Fig.2