- Joined

- Jan 22, 2008

- Messages

- 52,392

- Helped

- 14,748

- Reputation

- 29,778

- Reaction score

- 14,091

- Trophy points

- 1,393

- Location

- Bochum, Germany

- Activity points

- 297,965

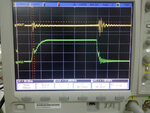

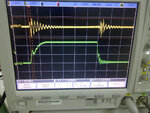

Rgate is very high now according to the waveform. A trade-off between oscillations and losses seems necessary.

I would build the circuit on a RF stripboard with a continuous copper plane on the top side (with voids around the drilled holes) and add low impedance bypass capacitors for in- and outputs.

I would build the circuit on a RF stripboard with a continuous copper plane on the top side (with voids around the drilled holes) and add low impedance bypass capacitors for in- and outputs.