alphus

Newbie level 6

- Joined

- Apr 21, 2014

- Messages

- 14

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 105

Hello.

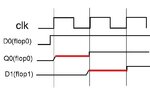

I'm trying to synthesize the SPI slave in RC Compiler. After synthesis occurs race conditions between SPI_CLK and system clock (clk):

How to avoid the race conditions in this case?

I'm trying to synthesize the SPI slave in RC Compiler. After synthesis occurs race conditions between SPI_CLK and system clock (clk):

Code:

always @(posedge clk)

spi_clk_r <= spi_clk;How to avoid the race conditions in this case?

Last edited: