samster19

Newbie

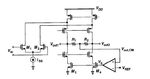

Hi, in the image above (taken from Design of CMOS Analog Design Circuits by Razavi), a high gain amplifier is used to provide common mode sense and feeback by controlling the current through M3 and M4. The idea is that if both Vout1 and Vout2 rise, then Ve rises, and the current through M3 and M4 rises, which then brings down the output common mode level.

Now I just want to know if my understanding of why exactly this brings the common mode level down is correct. Please correct me if my explanation below is wrong.

Raising Ve will raise the current through M3 and M4, but the transistors stacked on top are biased for a different current (their gate voltages are set). To satisfy KCL at Vout1 and Vout2, the drain voltages move down so that the same currents flow through the cascode PMOS and NMOS transistors and M3 and M4.

In other words, the voltages rise or fall to favor equal currents throughout the branch except for the top PMOS transistors, above the folding node.

I hope my explanation makes sense. Do correct me if I am wrong.