barry

Advanced Member level 7

- Joined

- Mar 31, 2005

- Messages

- 6,333

- Helped

- 1,194

- Reputation

- 2,400

- Reaction score

- 1,389

- Trophy points

- 1,393

- Location

- California, USA

- Activity points

- 34,476

Isn't a Schmitt trigger AND gate a digital gate?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Isn't a Schmitt trigger AND gate a digital gate?

Cant you use a spice model?

Are you designing a chip? That would have helped if you mentioned it 50 posts ago.

You never mentioned IC design, just designing a circuit. I asked about the intended technology but the question wasn"t answered. It was obvious to me that the discussed implementation with 100 ms RC time constant is inappropriate for IC implementation. You better study the design of industry standard reset generators.

if you could tell me what is a schmitt AND gate it would be great

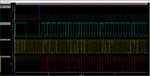

ok one last question, is there a way to stretch it digitally for around 100ns only without having to use the RC?

Something like this. You have to take the timing between the pulse and clock into consideration, but this is the general idea.View attachment 153923