Sujith Zis

Newbie level 3

- Joined

- Jan 17, 2014

- Messages

- 4

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 33

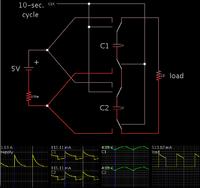

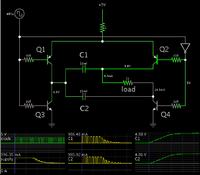

I needed to make a supercap battery bank circuit with >>5V input connected to, two 5.4V supercapacitors connected in series , and output from supercapacitors with on/off switch.<< Its harder the way I did it

also will i be able to get 10V Vout after fully charging the supercapacitors

also will i be able to get 10V Vout after fully charging the supercapacitors