gatzrulz

Newbie level 5

- Joined

- Oct 20, 2009

- Messages

- 8

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- India

- Activity points

- 1,349

Hi Frnds,

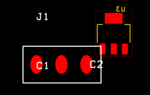

Im designing a PCB with Orcad Capture for Circuit and Orcad Layout Plus for PCB Designing. i have created a SMD Component using Library Manager and the photo is attached.

It was done using SSTOP, TOP, SPTOP, SMTOP.

Question No 1

Can i use the Opposite command by right clicking on the component, to use it at the bottom of the PCB.

Question No 2

When i place a SMD Component on TOP layer i couldnt able to place another component on the BOTTOM layer just exactly back side to the component placed on TOP Layer. Its showing a Unable to Clear or Verify DRC.

Thanks In Advance.

Im designing a PCB with Orcad Capture for Circuit and Orcad Layout Plus for PCB Designing. i have created a SMD Component using Library Manager and the photo is attached.

It was done using SSTOP, TOP, SPTOP, SMTOP.

Question No 1

Can i use the Opposite command by right clicking on the component, to use it at the bottom of the PCB.

Question No 2

When i place a SMD Component on TOP layer i couldnt able to place another component on the BOTTOM layer just exactly back side to the component placed on TOP Layer. Its showing a Unable to Clear or Verify DRC.

Thanks In Advance.