yeya

Newbie

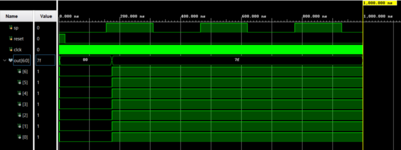

I am implementing a TDC TDL on Artix 7 and I need an encoder to convert the thermometer code to binary code using an encoder. I did my research on several encoder approaches and ultimately chose to work with the priority encoder due to its effectiveness against bubble errors. it is a 7 bit 128 encoder. When I synthesized the TOP module (TDC+ENCODER), the encoder output of the submodule is changed (Q instead of bin) and the output is always 7 after the first pulse of the input signal. I don't understand the reason. (I put the diagram below) This is my encoder code (I tried to do pipelining) I have also posted the TDC code and the TOP module and the simulation for anyone interested in helping me. Thanks a lot.