ee1

Full Member level 2

- Joined

- May 31, 2011

- Messages

- 120

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,298

- Activity points

- 2,036

Hi,

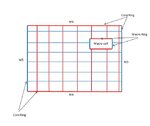

How should i connect my macro to power supply in top level?

should i create a power ring for the block in block level?

or just power strips will be enough?

I am working with Encounter.

Thanks!

How should i connect my macro to power supply in top level?

should i create a power ring for the block in block level?

or just power strips will be enough?

I am working with Encounter.

Thanks!