rishabh_31ec

Member level 1

Hi,

I am designing four stage NGCC opamp in TSMC 180 nm process using Cadence Mixed signal design domain, keeping all mos have uniform length

L = 360nm.

I have designed whole circuitry in proper way so as;

gm1 = 114µs & gmf1 = 113.87µs. ( gm1 = transconductance of PMOS of diffrential amplifier )

gm2 = 184µs & gmf2 = 183.5µs

gm3 = 294µs & gmf3 = 293.7µs

gm4 = 982µs.

but when I simulate my circuitry I have found that a pole appears very near to zero i.e. @ 50.97.

I have calculated by considering UGB is near to 3 MHz and second pole is @ 3UGB, third and fourth pole are@ 5UGB then how the pole appears @ 50.97 my dc gain is ≈102 dB.

Is this due to fact that,

dc gain x 3 db bandwidth ( determined by first pole ) = UGB

If yes then how can I remove my problem without degrading gain, else what is the exact problem and it solution?

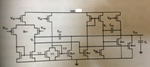

I have attached schematic of 3 stage NGCC just for idea.

I am designing four stage NGCC opamp in TSMC 180 nm process using Cadence Mixed signal design domain, keeping all mos have uniform length

L = 360nm.

I have designed whole circuitry in proper way so as;

gm1 = 114µs & gmf1 = 113.87µs. ( gm1 = transconductance of PMOS of diffrential amplifier )

gm2 = 184µs & gmf2 = 183.5µs

gm3 = 294µs & gmf3 = 293.7µs

gm4 = 982µs.

but when I simulate my circuitry I have found that a pole appears very near to zero i.e. @ 50.97.

I have calculated by considering UGB is near to 3 MHz and second pole is @ 3UGB, third and fourth pole are@ 5UGB then how the pole appears @ 50.97 my dc gain is ≈102 dB.

Is this due to fact that,

dc gain x 3 db bandwidth ( determined by first pole ) = UGB

If yes then how can I remove my problem without degrading gain, else what is the exact problem and it solution?

I have attached schematic of 3 stage NGCC just for idea.