wan

Junior Member level 2

Thanks for your help in advance.

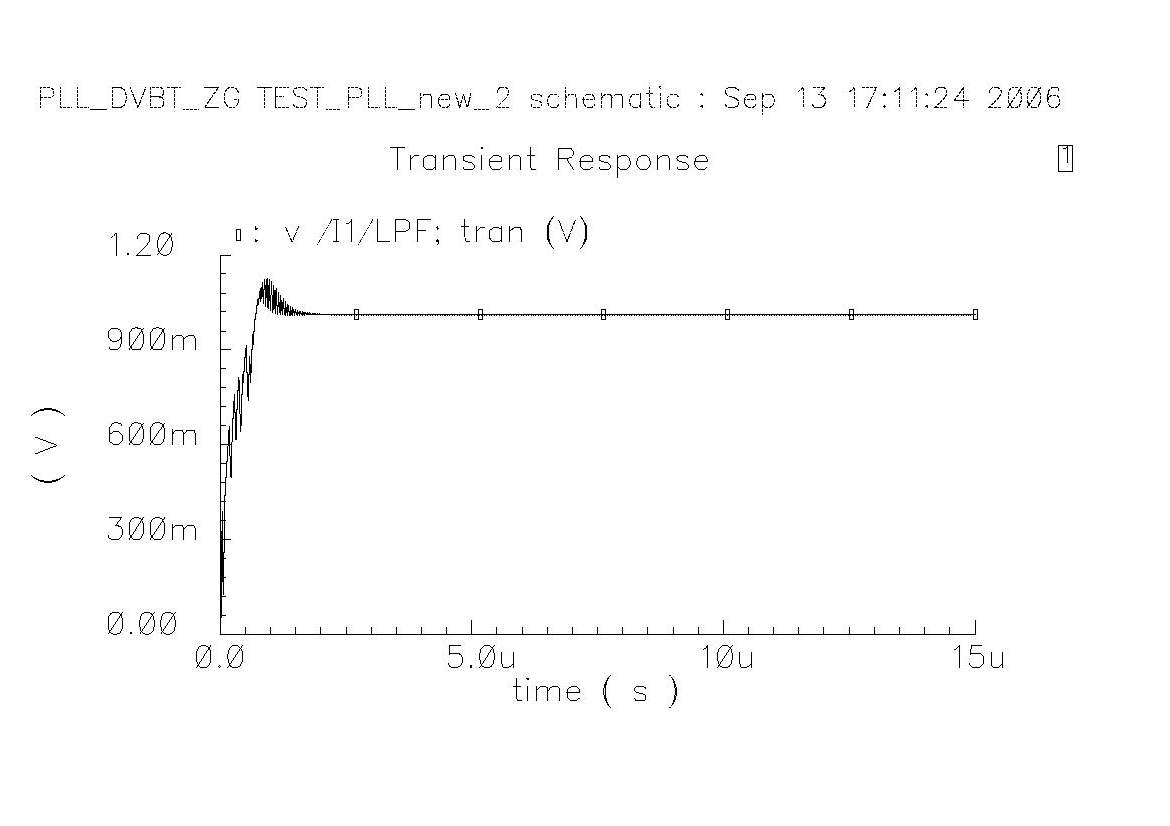

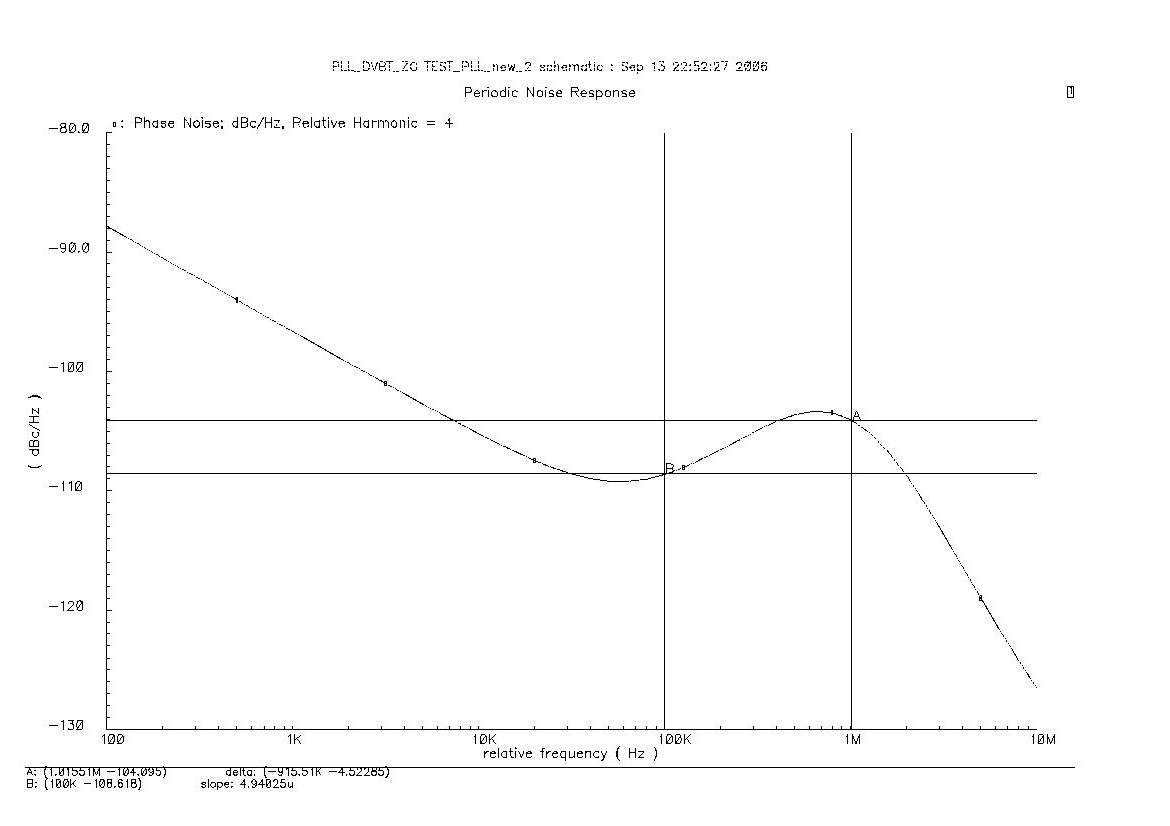

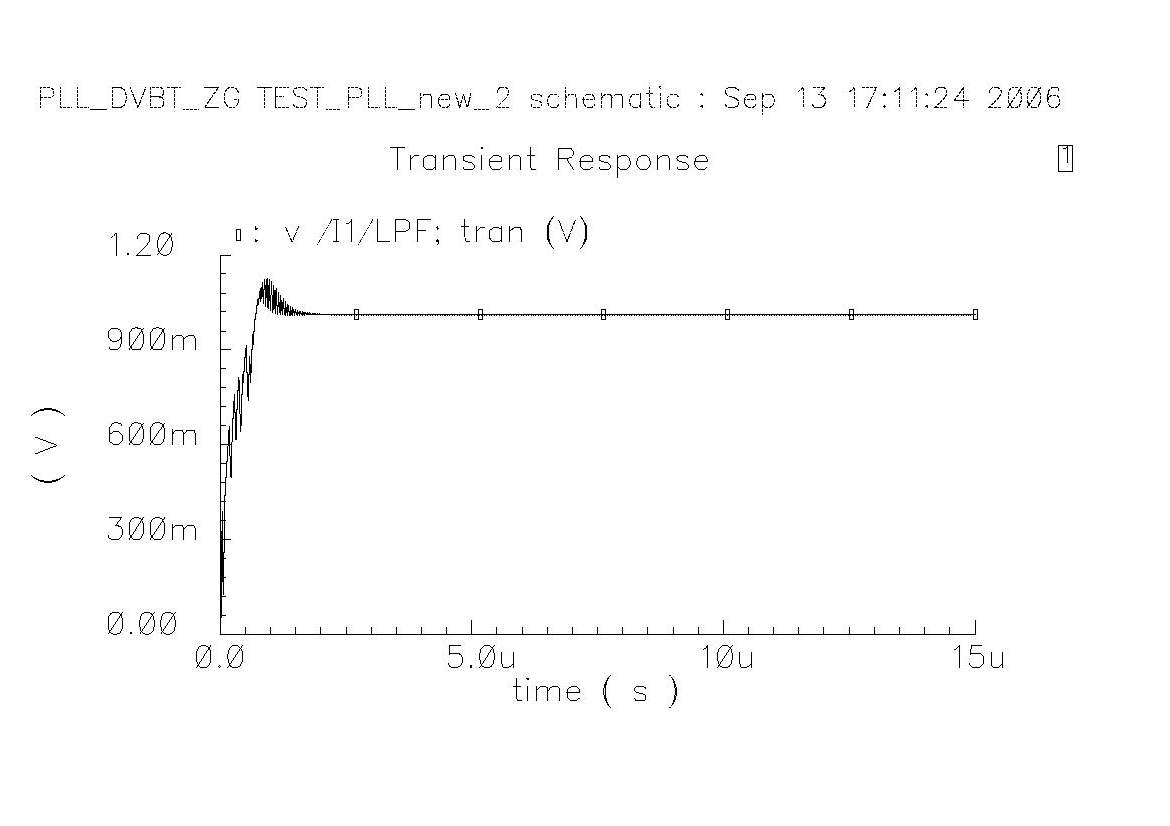

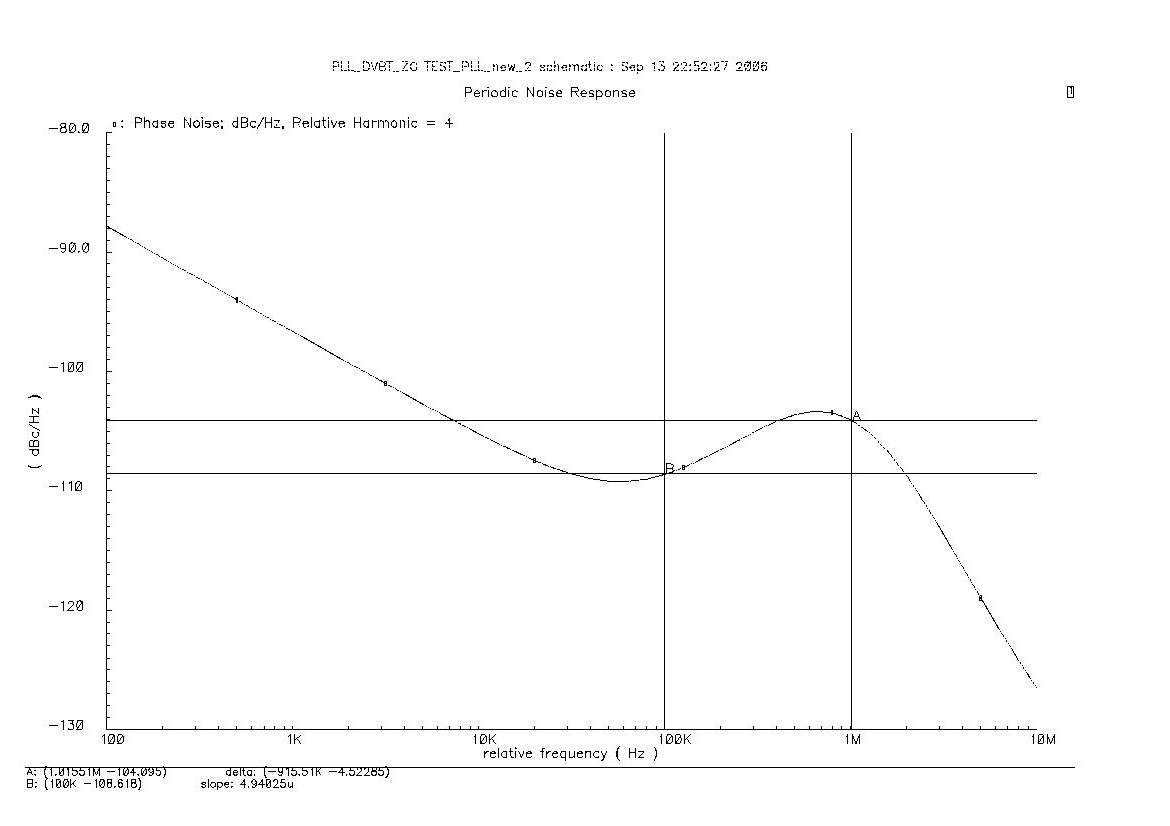

My reference clock is 20MHz,charge pump current is 50uA, Kvco is 380MHz/V,divider N is 12. I select loop bandwidth of 1.5Mhz, and the simulated trans and pnoise is as below. From the trans, the system is stable. But in the pnosie figure, I don't know why the curve increase from 100k to 1M. Does it make sense?

Thank your reply.

My reference clock is 20MHz,charge pump current is 50uA, Kvco is 380MHz/V,divider N is 12. I select loop bandwidth of 1.5Mhz, and the simulated trans and pnoise is as below. From the trans, the system is stable. But in the pnosie figure, I don't know why the curve increase from 100k to 1M. Does it make sense?

Thank your reply.