msdarvishi

Full Member level 4

Dear all,

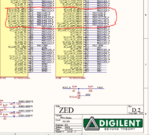

I am using Vivado2017 targeting a Zedboard including a Zynq-7000 (clg484) FPGA.

I am trying to transmit a signal as a clock between two FPGA Zedboards via FMC connectors. At the Destination board, I take the signal from an N-pin of FMC, and the synthesizer with apply an IBUF for that. Then I instantiated a BUFG in order to consider that signal as a clock to be fed to the flip-flops of my design. The design completely synthesized with no warning or error and also the implementation succeed with no errors, but I receive the following warning in implementation.

Can anyone help me to pass this issue?

Kind replies are in advance appreciated.

Regards,

I am using Vivado2017 targeting a Zedboard including a Zynq-7000 (clg484) FPGA.

I am trying to transmit a signal as a clock between two FPGA Zedboards via FMC connectors. At the Destination board, I take the signal from an N-pin of FMC, and the synthesizer with apply an IBUF for that. Then I instantiated a BUFG in order to consider that signal as a clock to be fed to the flip-flops of my design. The design completely synthesized with no warning or error and also the implementation succeed with no errors, but I receive the following warning in implementation.

Can anyone help me to pass this issue?

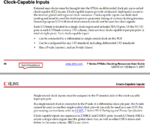

[DRC PLCK-12] Clock Placer Checks: Poor placement for routing between an IO pin and BUFG.

Resolution: Poor placement of an IO pin and a BUFG has resulted in the router using a non-dedicated path between the two. There are several things that could trigger this DRC, each of which can cause unpredictable clock insertion delays that result in poor timing. This DRC could be caused by any of the following: (a) a clock port was placed on a pin that is not a CCIO-pin (b)the BUFG has not been placed in the same half of the device or SLR as the CCIO-pin (c) a single ended clock has been placed on the N-Side of a differential pair CCIO-pin.

This is normally an ERROR but the CLOCK_DEDICATED_ROUTE constraint is set to FALSE allowing your design to continue. The use of this override is highly discouraged as it may lead to very poor timing results. It is recommended that this error condition be corrected in the design.

clksig_IBUF[10]_inst (IBUF.O) is locked to IOB_X1Y63

BUFG_inst11 (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y18

Kind replies are in advance appreciated.

Regards,