Saraadib

Member level 4

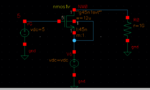

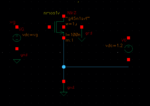

I want to measure on resistance of nmos and transmission gate ,I know on resistance is resistance of transistor when transistor is in triode region

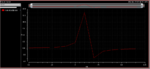

I have attached schematic of nmos transistor and transmission gate and plot on resistance of both, however result of them is wrong

Does any body have idea what is wrong with my circuit?

I have attached schematic of nmos transistor and transmission gate and plot on resistance of both, however result of them is wrong

Does any body have idea what is wrong with my circuit?

Attachments

Last edited: