Chenxin Jiang

Newbie

Hi,

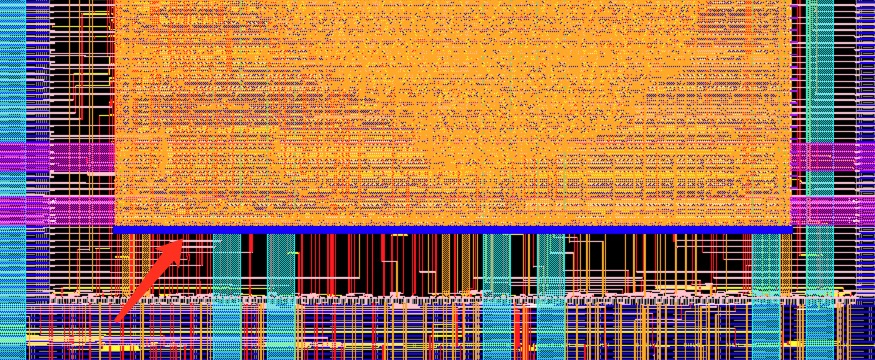

I was doing LVS check for my backend design. I use tsmc 28nm hpcp library and Innovus+Calibre flow.

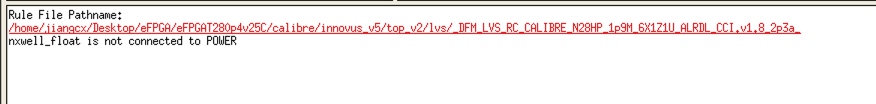

It tells me that there exits floating n_well in my design and my lvs check doesn't pass.

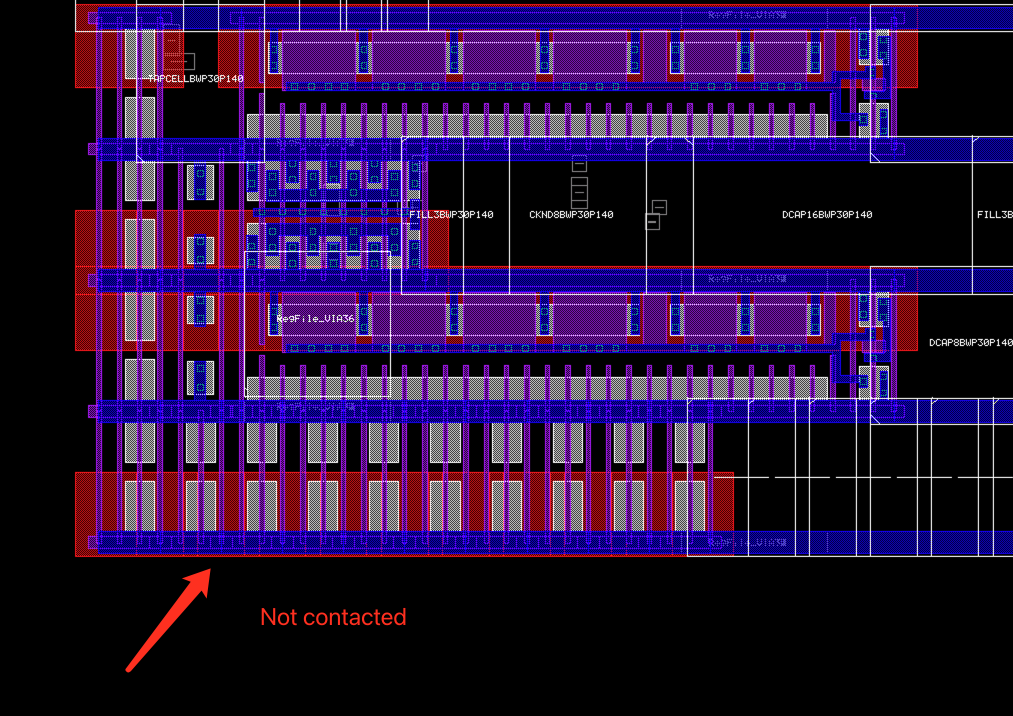

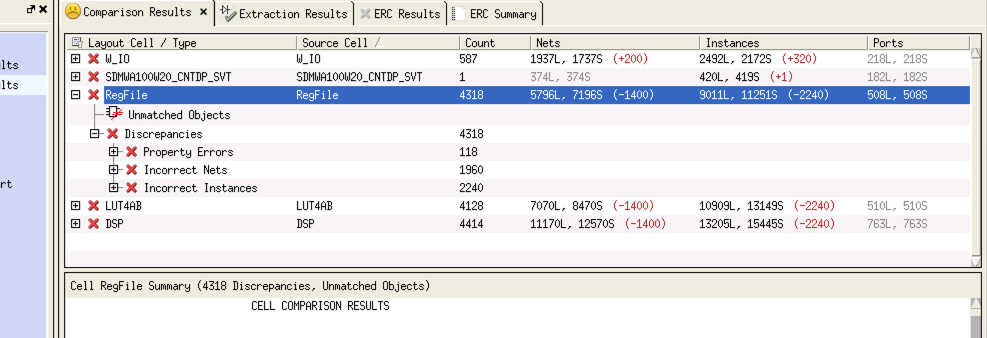

I found that the floating n_wells belong to the endcap along the block boundary inside the block(I use bottom up flow).

After I check the layout file, I notice that these n_wells have no contact with other n_wells, comparing with other rows.

The Innovus command is shown below

Could you please give me some idea?

Thanks!

I was doing LVS check for my backend design. I use tsmc 28nm hpcp library and Innovus+Calibre flow.

It tells me that there exits floating n_well in my design and my lvs check doesn't pass.

I found that the floating n_wells belong to the endcap along the block boundary inside the block(I use bottom up flow).

After I check the layout file, I notice that these n_wells have no contact with other n_wells, comparing with other rows.

The Innovus command is shown below

I guess my set up of adding physical cells in Innovus is wrong and I have attached the screenshots.set endcap_right "BOUNDARY_LEFTBWP30P140"

set endcap_left "BOUNDARY_RIGHTBWP30P140"

set endcap_top "BOUNDARY_LEFTBWP30P140 FILL2BWP30P140"

set endcap_bottom "BOUNDARY_LEFTBWP30P140 FILL2BWP30P140"

Could you please give me some idea?

Thanks!