JasonJung

Newbie

Hey,

I am just a newbie in asic design. ( I just started working as a PnR engineer)

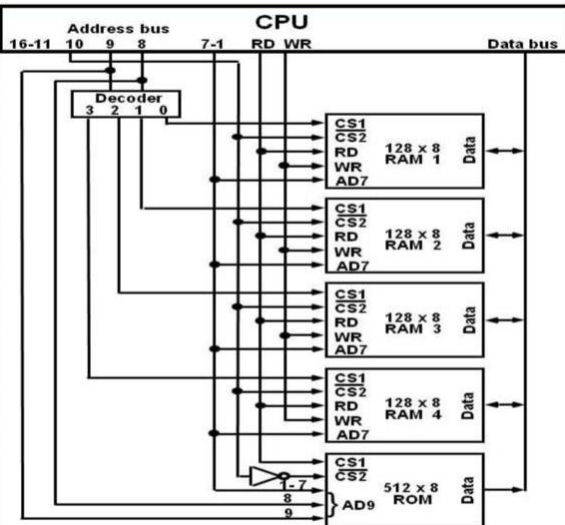

When I was in University, I remember that there was a concept of memory mapping... where several memory units share address bus and each emory unit is selected by some MSBs of address bits(Maybe the data in bus also shared). some thing like the below pic

The reason I suddenly thought about this was ... when I was working on my block.. there were so many memory macros and when I was placing those the fact I mentioned above hit my mind.

So my question is when there are many memorys in the block, will there be cases like the memory macros share the address bits or data bits ? (If yes i think its better to put those related ones close)

I am just a newbie in asic design. ( I just started working as a PnR engineer)

When I was in University, I remember that there was a concept of memory mapping... where several memory units share address bus and each emory unit is selected by some MSBs of address bits(Maybe the data in bus also shared). some thing like the below pic

The reason I suddenly thought about this was ... when I was working on my block.. there were so many memory macros and when I was placing those the fact I mentioned above hit my mind.

So my question is when there are many memorys in the block, will there be cases like the memory macros share the address bits or data bits ? (If yes i think its better to put those related ones close)