nana_7488

Member level 1

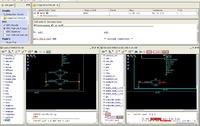

I'm using cmrf8sf V1.7.0.0DM, and based on the layer info, SXCUT_NET is for label purpose.

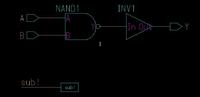

How I'm gonna add global sub! in schematic, is it with the subc device?sorry if this like dumb question to you..i just want to make sure I'm done it right.

Thanks

How I'm gonna add global sub! in schematic, is it with the subc device?sorry if this like dumb question to you..i just want to make sure I'm done it right.

Thanks