obeone

Newbie level 3

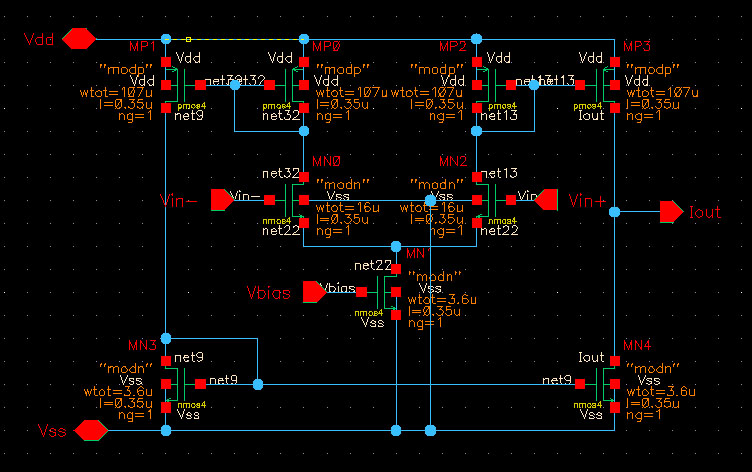

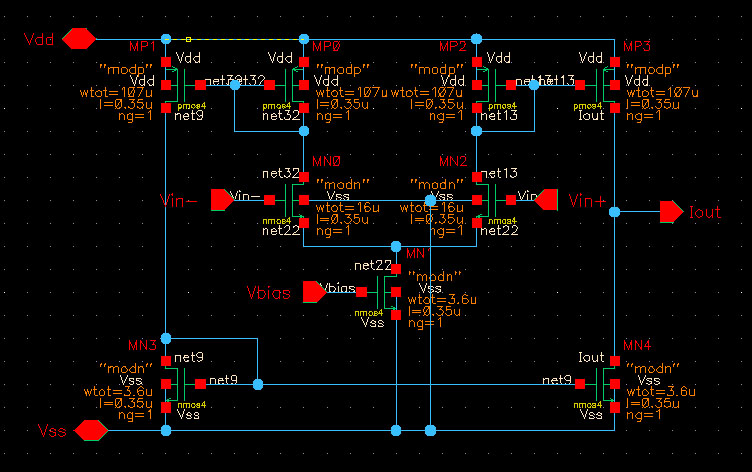

It is an conventional OTA.

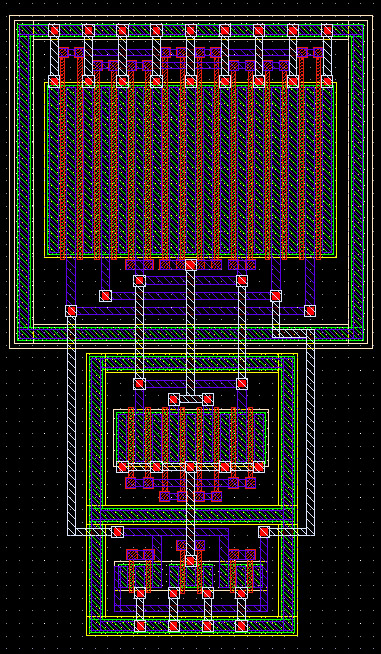

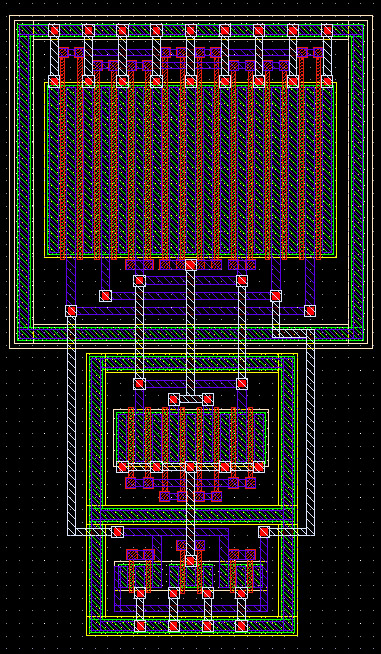

An aspect ratio of PMOS is 107u/0.35u , it is a long width ,so I use multifinger and layout techniques as interdigitation.

what do you think about it, please give me a comment and suggestion.

Best Regardly.

Obeone

An aspect ratio of PMOS is 107u/0.35u , it is a long width ,so I use multifinger and layout techniques as interdigitation.

what do you think about it, please give me a comment and suggestion.

Best Regardly.

Obeone