Disha Karnataki

Full Member level 5

- Joined

- Jul 20, 2013

- Messages

- 249

- Helped

- 9

- Reputation

- 18

- Reaction score

- 8

- Trophy points

- 18

- Location

- india

- Activity points

- 2,231

hey people,

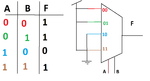

i started reading about multiplexers recently and could not understand implementation of logic gates using mux's. I got to know the methodology the way they have implemented certain functions say Ʃm(1,3,5,7,8,9,12) using 4:1 mux with a,b as select lines.

Here they form k-map and get out some Boolean expression and apply it to data lines or inputs where the Boolean expressions are in form of c,d.

i did not get after this i.e as per my knowledge Ʃm(1,3,5,7,8,9,12) means it's the sop equation and when i am realizing this function i should get out this function as a whole right?? Am i right?? Please help i am unable to understand this point that how exactly is the given sop equation realised......???

i started reading about multiplexers recently and could not understand implementation of logic gates using mux's. I got to know the methodology the way they have implemented certain functions say Ʃm(1,3,5,7,8,9,12) using 4:1 mux with a,b as select lines.

Here they form k-map and get out some Boolean expression and apply it to data lines or inputs where the Boolean expressions are in form of c,d.

i did not get after this i.e as per my knowledge Ʃm(1,3,5,7,8,9,12) means it's the sop equation and when i am realizing this function i should get out this function as a whole right?? Am i right?? Please help i am unable to understand this point that how exactly is the given sop equation realised......???