yefj

Advanced Member level 4

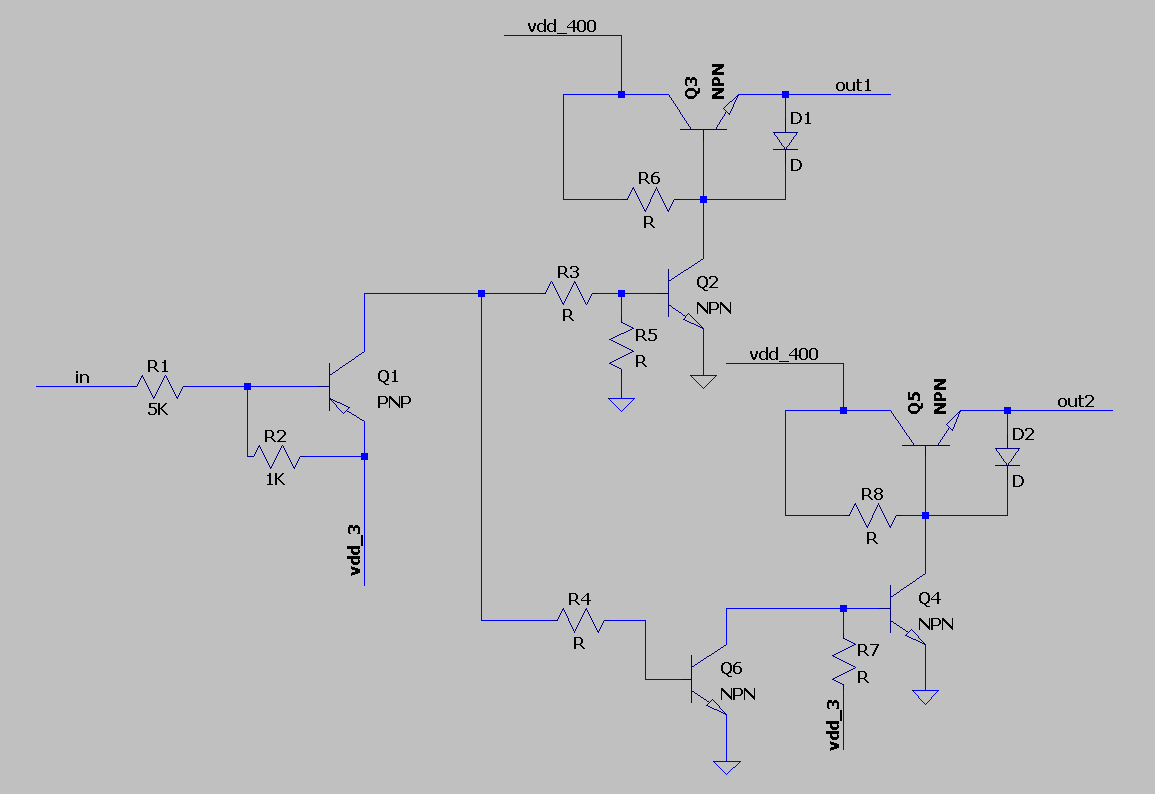

Hello,there is an intresting structure shown bellow, i can that there is a form of switch being used.

from mosfet i know that Vgate above Vt opens the transistor.

But here the bjt's are in weird forms .

how can i interpret the logic of this circuit?

Thanks.

from mosfet i know that Vgate above Vt opens the transistor.

But here the bjt's are in weird forms .

how can i interpret the logic of this circuit?

Thanks.