dpaul

Advanced Member level 5

Hi,

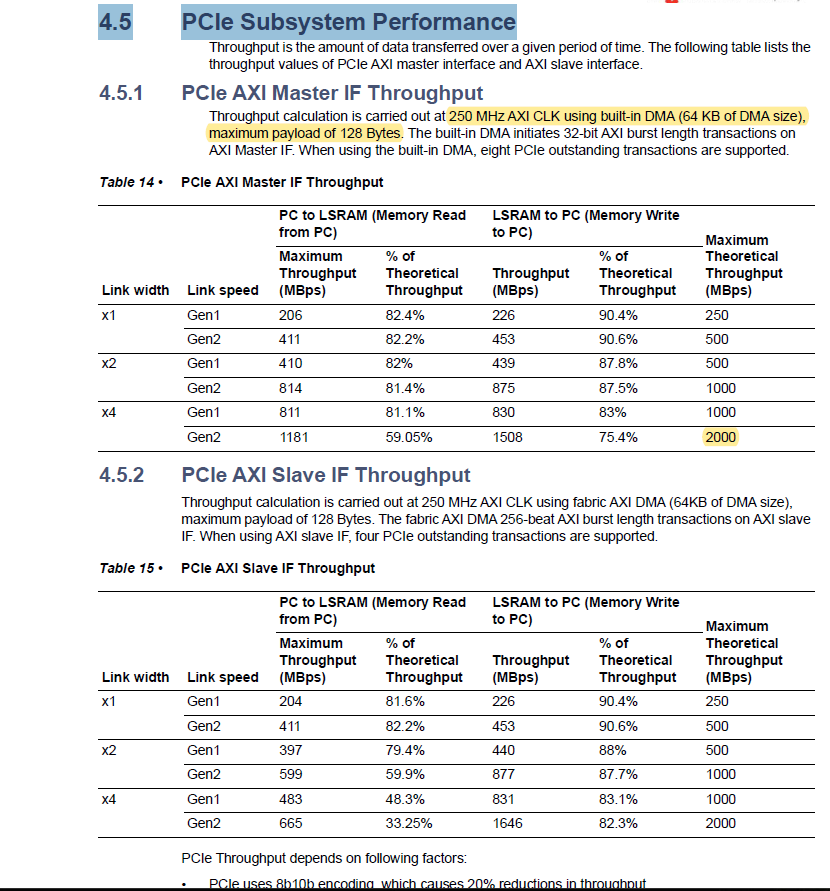

I am referring to the Microchip PCIe spec, UG0685 User Guide Revision 7.0, page 40, 4.5 PCIe Subsystem Performance.

I am considering the case of using PCIe v2.0 (5Gbps) x4 lanes. So the Maximum Theoretical Throughput (MBps) of 2000 listed in the above chart is calc as shown below:

5 Gbps x 4 = 20 Gbps = 2500 MBps. The spec also says that as v2.0 uses 8b10b encoding, so this causes a 20% reduction in throughput.

So Max Theoretical Throughput = 2500 - 500 = 2000 MBps.

I would like to know to effect on Max Theoretical Throughput value when I use a 100MHz AXI clock instead of the 250MHz AXI clock?

Can it be assumed that since the AXI clock is reduced to a value less than half, would the Max Theoretical Throughput be also reduced by bit lesser than 2000 MBps?

Else how can I roughly calc the Max Theoretical Throughput when the PCIe AXI4 clock is 100 MHz?

Note: I have already posted this on the Microchip FPGA forum, but anybody familiar with that forum knows what happens to the threads!

* also reduced by bit lesser than 2000 MBps?

also reduced by a bit lesser than half of 2000 MBps?

I am referring to the Microchip PCIe spec, UG0685 User Guide Revision 7.0, page 40, 4.5 PCIe Subsystem Performance.

I am considering the case of using PCIe v2.0 (5Gbps) x4 lanes. So the Maximum Theoretical Throughput (MBps) of 2000 listed in the above chart is calc as shown below:

5 Gbps x 4 = 20 Gbps = 2500 MBps. The spec also says that as v2.0 uses 8b10b encoding, so this causes a 20% reduction in throughput.

So Max Theoretical Throughput = 2500 - 500 = 2000 MBps.

I would like to know to effect on Max Theoretical Throughput value when I use a 100MHz AXI clock instead of the 250MHz AXI clock?

Can it be assumed that since the AXI clock is reduced to a value less than half, would the Max Theoretical Throughput be also reduced by bit lesser than 2000 MBps?

Else how can I roughly calc the Max Theoretical Throughput when the PCIe AXI4 clock is 100 MHz?

Note: I have already posted this on the Microchip FPGA forum, but anybody familiar with that forum knows what happens to the threads!

--- Updated ---

* also reduced by bit lesser

also reduced by a bit lesser than half of 2000 MBps?

Last edited: