Jorge Jesse Cantu

Junior Member level 1

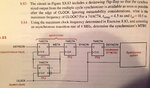

I have a question in my text book that I do not quite understand. I was wondering if someone could please explain what the question means? Such as, what is a deskewed flip flop. How would one find the max frequency of the clock from the diagram?

Below is the question (8.83) with the corresponding diagram at the bottom:

Below is the question (8.83) with the corresponding diagram at the bottom: