ravikiran1550

Newbie

- Joined

- Oct 29, 2013

- Messages

- 1

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- Jalandhar, India, India

- Activity points

- 1,284

Hi all,

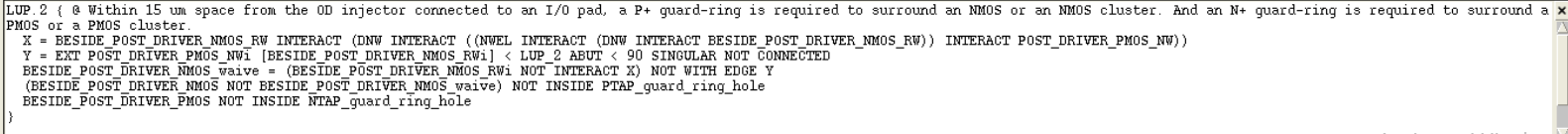

can you help on LUP.2 violations coming top of the CLAM cells. which are placed for ESD protection in the CHIP. i am getting LUP.2 Violation in the fullchip. fullchip has 10 macrons and it is coming from the one macro. and the macro has analog IP which is provided by the client. we tried removed all the power hooked to the macro but no luck, when we remove the signals Errors gone. but we have 250 pin are hooked up. how to find what is the issue is causing LUP.2. here i am attached screenshot.

can you help on LUP.2 violations coming top of the CLAM cells. which are placed for ESD protection in the CHIP. i am getting LUP.2 Violation in the fullchip. fullchip has 10 macrons and it is coming from the one macro. and the macro has analog IP which is provided by the client. we tried removed all the power hooked to the macro but no luck, when we remove the signals Errors gone. but we have 250 pin are hooked up. how to find what is the issue is causing LUP.2. here i am attached screenshot.