PhdSA

Newbie

Hello,

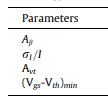

I am designing a current steering DAC based on technology TSMC 65 nm. I have a technology 65 nm CMOS TSMC in cadence. I asked how can i extract the mismatch technology parameters Avth and Aβ from this technology. I'm so gratefull if someone have these parameter send me a document.

Best Regards

I am designing a current steering DAC based on technology TSMC 65 nm. I have a technology 65 nm CMOS TSMC in cadence. I asked how can i extract the mismatch technology parameters Avth and Aβ from this technology. I'm so gratefull if someone have these parameter send me a document.

Best Regards