shlooky

Member level 2

Hi all,

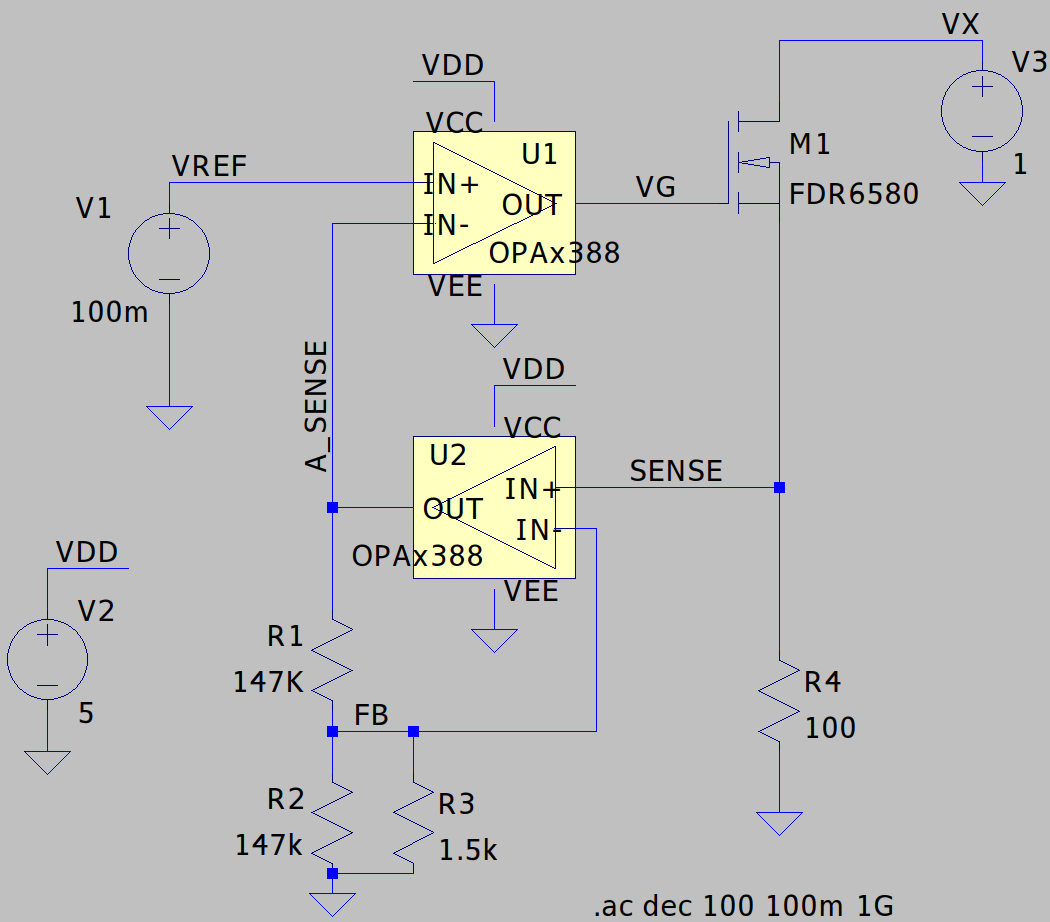

I am trying to analyze an active load circuit designed for the lowest current possible. Schematic in the picture.

I tried to amplify the sensed voltage (by 100 / 40dB) to increase the sensitivity. Yes, I know this circuit can easily oscillate...

My question is, which node should I split to break the loop for loop gain / AC analysis? Is it SENSE, A_SENSE or VG ?

I mean, standard AC simulation with DC source DC=0 AC=1 in the loop.

Thanks

Shlooky

I am trying to analyze an active load circuit designed for the lowest current possible. Schematic in the picture.

I tried to amplify the sensed voltage (by 100 / 40dB) to increase the sensitivity. Yes, I know this circuit can easily oscillate...

My question is, which node should I split to break the loop for loop gain / AC analysis? Is it SENSE, A_SENSE or VG ?

I mean, standard AC simulation with DC source DC=0 AC=1 in the loop.

Thanks

Shlooky