Riemann73

Newbie

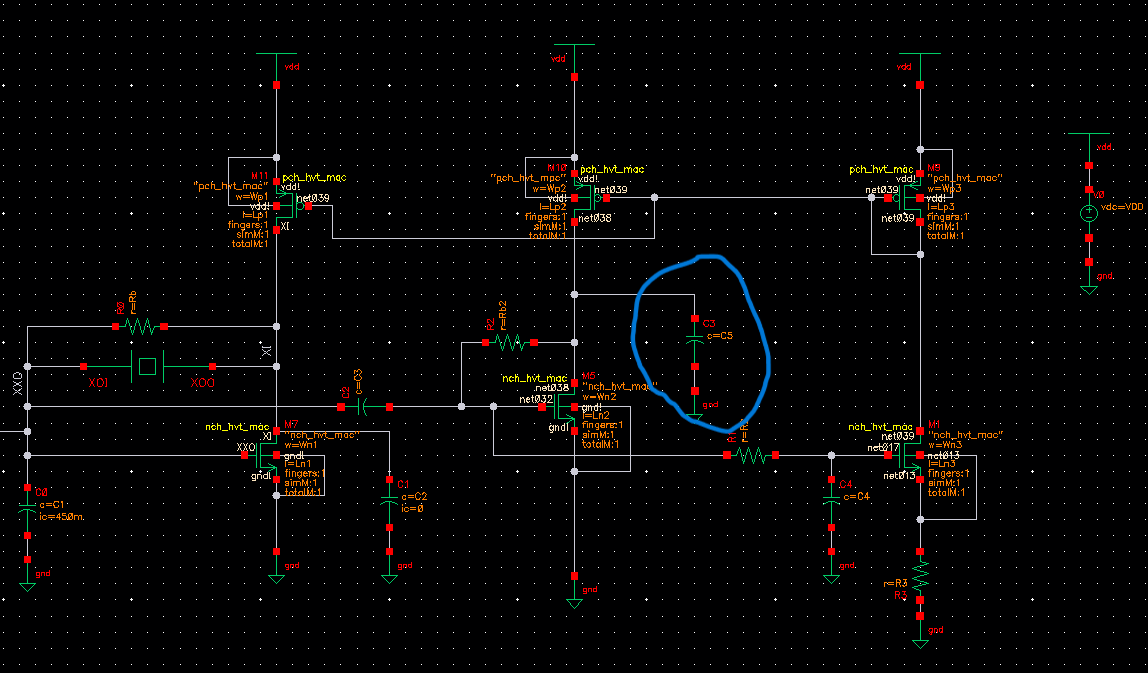

Hello , Currently I'm designing pierce oscillator 96Mhz with amplitude gain control circuit , the use for capacitor C5 was to limit the nmos drain ac variations to keep its bias point until the feedback regulates the loop and the oscillator bias current, the problem is a large degradation happens to the phase noise due to the presence of this cap , my question is why ? and how to deal with this