yefj

Advanced Member level 4

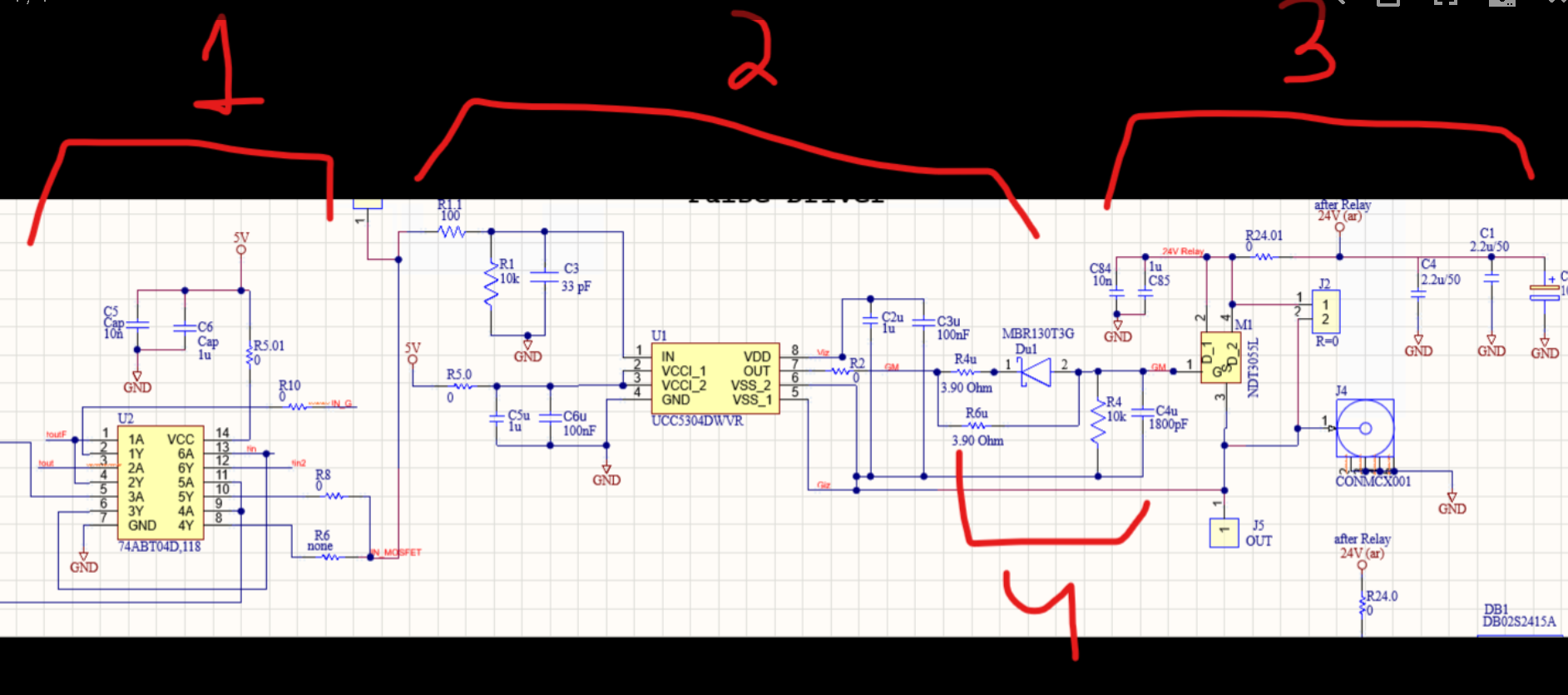

Hello, i have here a circuit shown bellow it has 4 parts.

part 1 consists of a HEX inverter

https://assets.nexperia.com/documents/data-sheet/74ABT04.pdf

Part2 has some buffer driver with component shown bellow.

https://www.ti.com/lit/ds/symlink/ucc5304.pdf?HQS=dis-mous-null-mousermode-dsf-pf-null-wwe&ts=1701024772623&ref_url=https%3A%2F%2Fwww.mouser.de%2F

Part 3 is a mosfet

https://www.onsemi.com/pdf/datasheet/ndt3055l-d.pdf

https://www.onsemi.com/products/discrete-power-modules/mosfets/NDT3055L#technical-documentation

Part 4 : has a diode connected in a loop

Could you please say the general dynamics of this circuit?

how these parts play together?

Thanks.

part 1 consists of a HEX inverter

https://assets.nexperia.com/documents/data-sheet/74ABT04.pdf

Part2 has some buffer driver with component shown bellow.

https://www.ti.com/lit/ds/symlink/ucc5304.pdf?HQS=dis-mous-null-mousermode-dsf-pf-null-wwe&ts=1701024772623&ref_url=https%3A%2F%2Fwww.mouser.de%2F

Part 3 is a mosfet

https://www.onsemi.com/pdf/datasheet/ndt3055l-d.pdf

https://www.onsemi.com/products/discrete-power-modules/mosfets/NDT3055L#technical-documentation

Part 4 : has a diode connected in a loop

Could you please say the general dynamics of this circuit?

how these parts play together?

Thanks.