mahaju

Full Member level 2

Hi

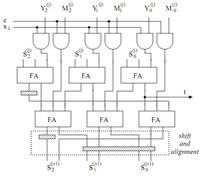

If a number is in carry save notation how do I shift it?

A number in normal binary notation when shifted right, would cause the LSB to go out of the number and the MSB to be padded with zero or the sign bit

But if the number is in redundant Carry-Save format, how do I shift it?

I desperately need help in this

I have been trying to look for this since quite a few days and non of the forums are helping me in any way

Thanks in advance

If a number is in carry save notation how do I shift it?

A number in normal binary notation when shifted right, would cause the LSB to go out of the number and the MSB to be padded with zero or the sign bit

But if the number is in redundant Carry-Save format, how do I shift it?

I desperately need help in this

I have been trying to look for this since quite a few days and non of the forums are helping me in any way

Thanks in advance