rezadevelop

Newbie level 3

- Joined

- Jul 19, 2009

- Messages

- 3

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,296

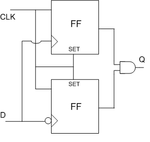

i have problem with characterization of complex cell.

my cell is complex & i can't use one ff or latch!

my cell.otp:

-----

my ncx: Liberty NCX version C-2009.06-SP1

i think i can't use "ncx_multiple_descriptor".

I'm sure I'm doing something wrong, but don't know exactly where it is.

Thanks in advance

my cell is complex & i can't use one ff or latch!

my cell.otp:

Code:

pin D {

direction : input ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

}

pin L2 {

direction : input ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

}

pin CKM {

direction : input ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

}

pin RET {

direction : input ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

}

pin CKLC {

direction : input ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

}

pin CKL2 {

direction : input ;

ncx_hold_rising_rise_constrained_pin_transition_index : 0 ;

ncx_hold_rising_fall_constrained_pin_transition_index : 0 ;

ncx_hold_rising_rise_related_pin_transition_index : 0 ;

ncx_hold_rising_fall_related_pin_transition_index : 0 ;

ncx_setup_rising_rise_constrained_pin_transition_index : 0 ;

ncx_setup_rising_fall_constrained_pin_transition_index : 0 ;

ncx_setup_rising_rise_related_pin_transition_index : 0 ;

ncx_setup_rising_fall_related_pin_transition_index : 0 ;

}

pin Sn {

direction : output ;

internal_node : IQ;

ncx_internal_power_rise_input_transition_time_index : 1 ;

ncx_internal_power_fall_input_transition_time_index : 1 ;

ncx_internal_power_rise_total_output_net_capacitance_index : 0 ;

ncx_internal_power_fall_total_output_net_capacitance_index : 0 ;

ncx_rising_edge_rise_input_net_transition_index : 1 ;

ncx_rising_edge_fall_input_net_transition_index : 1 ;

ncx_rising_edge_rise_total_output_net_capacitance_index : 0 ;

ncx_rising_edge_fall_total_output_net_capacitance_index : 0 ;

}

pin Sp {

direction : output ;

internal_node : IQN;

ncx_internal_power_rise_input_transition_time_index : 1 ;

ncx_internal_power_fall_input_transition_time_index : 1 ;

ncx_internal_power_rise_total_output_net_capacitance_index : 0 ;

ncx_internal_power_fall_total_output_net_capacitance_index : 0 ;

ncx_rising_edge_rise_input_net_transition_index : 1 ;

ncx_rising_edge_fall_input_net_transition_index : 1 ;

ncx_rising_edge_rise_total_output_net_capacitance_index : 0 ;

ncx_rising_edge_fall_total_output_net_capacitance_index : 0 ;

}

pg_pin VDD {

voltage_name : VDD ;

pg_type : primary_power ;

}

pg_pin VSS {

voltage_name : VSS ;

pg_type : primary_ground ;

}

ncx_optimization {

}

statetable("D L2 CKM CKLC CKL2 RET","IQ IQN"){

table : "- - - - - 1 : - - : H L,\

L/H H/L - 1 - 0 : - - : L H,\

L/H L/H - 1 - 0 : - - : N N,\

r - 1 - - 0 : - - : L H,\

f - 1 - - 0 : - - : L H,\

L/H - 1 - - 0 : - - : N N,\

- L/H - - 0 0 : - - : N N,\

- r - - 0 0 : - - : L H,\

- f - - 0 0 : - - : L H ";

}-----output result:

reading /home/.../TD_X1.opt...

Error: statetable(D L2 CKM CKLC CKL2 RET,IQ IQN) is not a valid group of cell. (NCXPS-22)

correct errors in /home/.../TD_X1.opt and rerun

cell types:

combinational : 1

pruning inactive cells...[0] done

done

Error: failed library database initialization (NCXDB-5)

my ncx: Liberty NCX version C-2009.06-SP1

i think i can't use "ncx_multiple_descriptor".

I'm sure I'm doing something wrong, but don't know exactly where it is.

Thanks in advance

Last edited by a moderator: