pkaras

Junior Member level 1

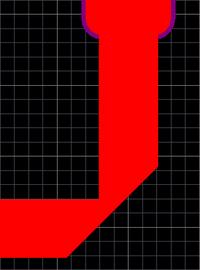

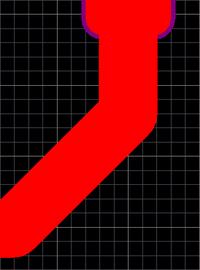

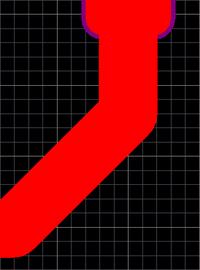

I am trying to draw an impedance (50 Ohm) controlled trace. I am going to use coplanar waveguide. I have read that chamfering is the recommended method for bends.

I have calculated that I need to use 40 mil wide trace and I need to leave gaps of 8 mil. I have also calculated M (percentage chamfer), which supposed to be ~78 (conductor height is 60 mil).

I would like to know if I did everything correctly. I am using chamfering technique for the first time and it seems a bit unusual to see the bend so thin.

I attach two images where one shows regular 40 mil wide trace and another shows trace that is chamfered. Does it look like it supposed to be?

Btw, ground plane is not displayed.

I have calculated that I need to use 40 mil wide trace and I need to leave gaps of 8 mil. I have also calculated M (percentage chamfer), which supposed to be ~78 (conductor height is 60 mil).

I would like to know if I did everything correctly. I am using chamfering technique for the first time and it seems a bit unusual to see the bend so thin.

I attach two images where one shows regular 40 mil wide trace and another shows trace that is chamfered. Does it look like it supposed to be?

Btw, ground plane is not displayed.