ABO_ATHAB

Junior Member level 1

- Joined

- Dec 19, 2011

- Messages

- 16

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,403

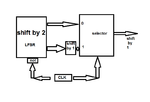

hi every one

today during trying implement dual edge counter i find this post

https://www.edaboard.com/threads/133082/

one of the member add code that work very well , here is the simulink

https://obrazki.elektroda.pl/98_1289953468.gif

can any one help ous and post code or share idea for dual edge LFSR random generator

https://en.wikipedia.org/wiki/Linear_feedback_shift_register

best regards:

m.s

today during trying implement dual edge counter i find this post

https://www.edaboard.com/threads/133082/

one of the member add code that work very well , here is the simulink

https://obrazki.elektroda.pl/98_1289953468.gif

can any one help ous and post code or share idea for dual edge LFSR random generator

https://en.wikipedia.org/wiki/Linear_feedback_shift_register

best regards:

m.s