Electrowizard

Newbie level 5

Hello,

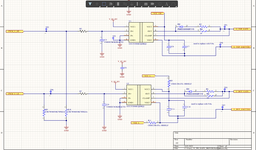

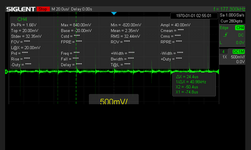

I am building a high voltage inverter operating at 200v. i am using isolated gate drivers and the supply for the gate drivers (15V) is also isolated. But the inverter switching causes a voltage spike in the gate driver power supply . the spike is happening at 40khz which is twice the switching frequency of the inverter. I have dc link capacitors and mlcc filtercaps attached to the dc line

Can someone help me figure out why the inverter switching noise is propagating to the low voltage side.

Thank you

I am building a high voltage inverter operating at 200v. i am using isolated gate drivers and the supply for the gate drivers (15V) is also isolated. But the inverter switching causes a voltage spike in the gate driver power supply . the spike is happening at 40khz which is twice the switching frequency of the inverter. I have dc link capacitors and mlcc filtercaps attached to the dc line

Can someone help me figure out why the inverter switching noise is propagating to the low voltage side.

Thank you