biswaIITH

Full Member level 4

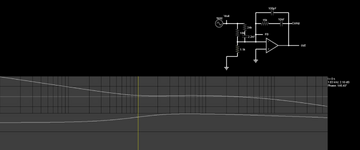

We are facing an issue where the output of the DC-DC(12V) drops to 1-2 V for few milliseconds when an SOM module tries connecting with the cloud. The DC-DC is designed using LM5146 IC from texas instruments

This is mostly due to RF noise we suspect.

Can anyone suggest any shielding technique to prevent the above?

This is mostly due to RF noise we suspect.

Can anyone suggest any shielding technique to prevent the above?