Danielye

Junior Member level 3

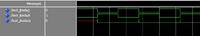

How to implement this logic in VHDL

the logic table is as follows,

K J out

H/L rise edge H

rise edge H/L L

H/L fall edge No change

fall edge H/L No change

Thanks in advance!

the logic table is as follows,

K J out

H/L rise edge H

rise edge H/L L

H/L fall edge No change

fall edge H/L No change

Thanks in advance!