juliewxh

Newbie

Hello everyone,

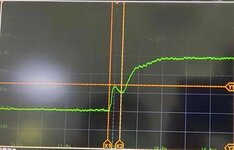

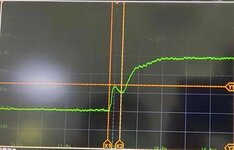

I encountered an issue that the clock signal got some noises on its edges during the transition (as is shown in the picture).

It seems it's because the power supply has some ripples caused by the digital circuit's instantaneous power. The noises are big enough to make the flip-flops toggle like there are true clock edges.

Which will be a good way to deal with this condition? Filtering the noise on the clock using a digital circuit, suppressing the noise using a capacitance, applying some strategies to enhance the stability of the power, or are there any general approaches to solve this issue?

Any suggestion will be appreciated.

Thank you very much!

I encountered an issue that the clock signal got some noises on its edges during the transition (as is shown in the picture).

It seems it's because the power supply has some ripples caused by the digital circuit's instantaneous power. The noises are big enough to make the flip-flops toggle like there are true clock edges.

Which will be a good way to deal with this condition? Filtering the noise on the clock using a digital circuit, suppressing the noise using a capacitance, applying some strategies to enhance the stability of the power, or are there any general approaches to solve this issue?

Any suggestion will be appreciated.

Thank you very much!

Last edited: