mostafah67

Member level 1

- Joined

- Jun 2, 2013

- Messages

- 39

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Activity points

- 1,575

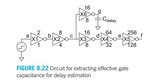

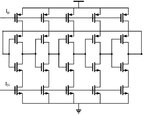

i need to know the output capacitance in a output of each stage of a cmos ring oscillator, i know the capacitance is voltage dependent but i need a value for my calculation, i can calculate the capacitance by hand calculations (by using of formulas from digital integrated circuits,by john.M rabaey) but i don't know how they are close to the actual value!

is there a way that i can calculate the capacitance using HSPICE or another software?

is there a way that i can calculate the capacitance using HSPICE or another software?

Last edited: