girih192002

Full Member level 2

Hi,

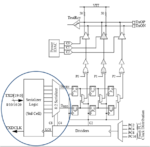

I am just confusing with below attached picture. I have some doubt. This is SerDes architecture.

1. Here How 8b/10b and 16b/20b encoded signal is converted into 8:2 multiplexer ? actually ODD parallel inputs to EVEN parallel outputs

2. Why do we need to generated always ODD and EVEN signal at output of Serializer ?

If you have any architecture for 8b/10b encoding then, please, suggest me those pipelin topoloy papers.

thank you

I am just confusing with below attached picture. I have some doubt. This is SerDes architecture.

1. Here How 8b/10b and 16b/20b encoded signal is converted into 8:2 multiplexer ? actually ODD parallel inputs to EVEN parallel outputs

2. Why do we need to generated always ODD and EVEN signal at output of Serializer ?

If you have any architecture for 8b/10b encoding then, please, suggest me those pipelin topoloy papers.

thank you