jjeevan007

Full Member level 5

- Joined

- Apr 13, 2012

- Messages

- 310

- Helped

- 44

- Reputation

- 88

- Reaction score

- 43

- Trophy points

- 1,308

- Location

- bangalore

- Activity points

- 2,782

hi to all,

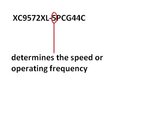

i am very new to CPLD i want to design the XC9572XL board, i don't where to start,

please can any one give me basic set up circuit of the XC9572XL,

i have gone through the datasheet but i am not able to get anything......

i have one more doubt the thus it requires any crystal oscillator or not..... just like in microcontroller...

or it has in built oscillator.....

if external oscillator is required than to which pin we have to supply.........

please help

i am very new to CPLD i want to design the XC9572XL board, i don't where to start,

please can any one give me basic set up circuit of the XC9572XL,

i have gone through the datasheet but i am not able to get anything......

i have one more doubt the thus it requires any crystal oscillator or not..... just like in microcontroller...

or it has in built oscillator.....

if external oscillator is required than to which pin we have to supply.........

please help