andrea22

Junior Member level 2

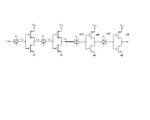

Does anyone have any tutorial about cmos tg dynamic shift register?

I need an explaination how this circuit works.

What I ment why this circuit only works with non-overlapping clocks,

or why this circuit can't work with overlapping clocks?

I need to prove why this circuit can't work with overlapping clocks.

I need an explaination how this circuit works.

What I ment why this circuit only works with non-overlapping clocks,

or why this circuit can't work with overlapping clocks?

I need to prove why this circuit can't work with overlapping clocks.