danadakk

Advanced Member level 6

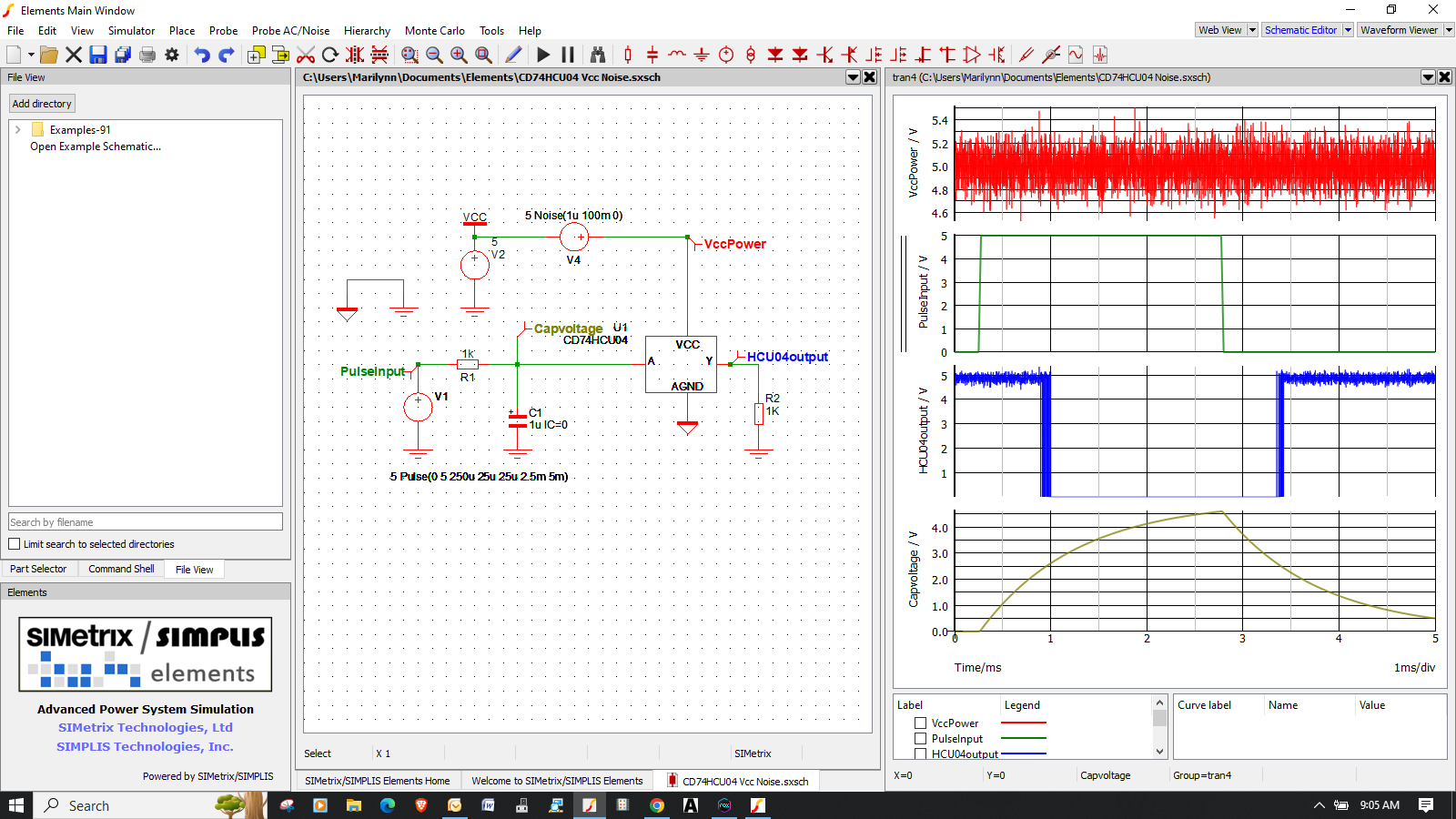

100 mV RMS on Vcc, coupled with slow rise time CMOS inputs, lots of output jitter -

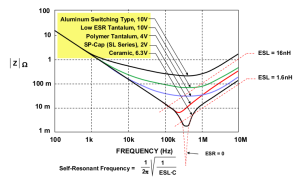

Bypass capacitor ESR crucial, as well as Tr, Tf of the applicable input/gate.

e2e.ti.com

e2e.ti.com

Regards, Dana.

Regards, Dana.

Bypass capacitor ESR crucial, as well as Tr, Tf of the applicable input/gate.

[FAQ] How do I select a bypass capacitor for a CMOS logic device? - Logic forum - Logic - TI E2E support forums

Other Parts Discussed in Thread: SN74LVC1G08 , SN74LVC16244A FAQ: Logic and Voltage Translation > Power and Thermals >> Current FAQ For the short answer - use

Regards, Dana.

Regards, Dana.