husamsdu

Member level 1

Dear RealAEL ,

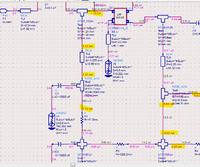

I used R1 and R2 for biasing. I used 0.6V bias source for simulation even so but there was no result again. What can be the reason, what mistake i did?

I simulated s-parameters on AWR so i need just OIP3,IIP3,P1dB and K.

Also i added two tone harmonicsimulation but i haven't connect anything to it. Will i connect .s2p file and how?

Thank you.

I used R1 and R2 for biasing. I used 0.6V bias source for simulation even so but there was no result again. What can be the reason, what mistake i did?

I simulated s-parameters on AWR so i need just OIP3,IIP3,P1dB and K.

Also i added two tone harmonicsimulation but i haven't connect anything to it. Will i connect .s2p file and how?

Thank you.

Last edited: