mobinmk

Full Member level 2

- Joined

- May 27, 2010

- Messages

- 140

- Helped

- 4

- Reputation

- 8

- Reaction score

- 4

- Trophy points

- 1,298

- Location

- Kollam (Quilon),kerala, India

- Activity points

- 2,484

Hi frndz,

am new bie here.

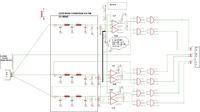

i wana to make variable frequency drive for 3 phase induction motor.

succesfully, i generate 3 pwm pulses using DDS by arduino uno.

nw i wana to make INVERT of 3 pulses.

spwm frequency is 33khz

first itz is fed into 12.5khz lowpass chebysck filter.

the output is fed into lm339 comparator.

vcc is 5v

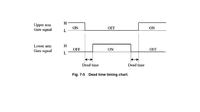

output of the comparator gives two pulse which will AND ED WITH ORGINAL SPWM PULSES. USING 2 nand gate ic

i cant understant frm the lm339 comparator.

dc reference voltage by resistors fed into 3.3v??

output of comparator is connected with 2 resistor.in middle point =3.3v

why this 2 resistor is connected across the output of comparator.???

pls reply.

regardz

mobin

am new bie here.

i wana to make variable frequency drive for 3 phase induction motor.

succesfully, i generate 3 pwm pulses using DDS by arduino uno.

nw i wana to make INVERT of 3 pulses.

spwm frequency is 33khz

first itz is fed into 12.5khz lowpass chebysck filter.

the output is fed into lm339 comparator.

vcc is 5v

output of the comparator gives two pulse which will AND ED WITH ORGINAL SPWM PULSES. USING 2 nand gate ic

i cant understant frm the lm339 comparator.

dc reference voltage by resistors fed into 3.3v??

output of comparator is connected with 2 resistor.in middle point =3.3v

why this 2 resistor is connected across the output of comparator.???

pls reply.

regardz

mobin