roki

Member level 1

Hi everyone,

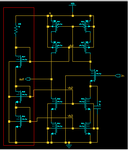

Attached is the OTA schematic i've drawn.

My first question is whether the type of current mirror(red boxed) i used to generate a cascode bias voltage is correct or incorrect?

Then next, i need help in designing all transistors to be in saturation.I tried myself numerous times, but kept failing.

Highly, the way i calculated it is very wrong.The supply voltage is 1.2V, thus it does make it harder to design due to small headroom.

Bias current is 1uA.Kindly assist me in designing all transistors to be saturation.

Thanks

Attached is the OTA schematic i've drawn.

My first question is whether the type of current mirror(red boxed) i used to generate a cascode bias voltage is correct or incorrect?

Then next, i need help in designing all transistors to be in saturation.I tried myself numerous times, but kept failing.

Highly, the way i calculated it is very wrong.The supply voltage is 1.2V, thus it does make it harder to design due to small headroom.

Bias current is 1uA.Kindly assist me in designing all transistors to be saturation.

Thanks