CandleCookie

Advanced Member level 4

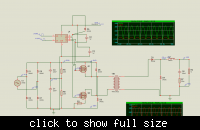

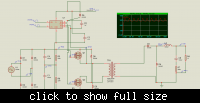

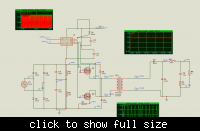

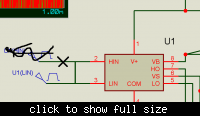

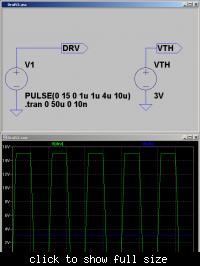

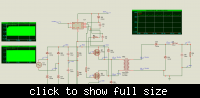

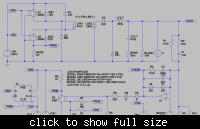

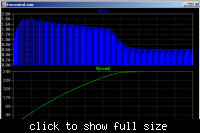

Hi, Genome. Unfortunately, the transformer that I'm using need to have that connection. Now, I have changed a new transformer. The primary Vp=340V and Vs=48V. So, Lp=6.5mH and Ls=130uH. Below are the circuit and waveforms I obtained. I can get roughly 45Vpeak but referring above, you mentioned that the output should be 24V due to the 50% duty cycle. But do this duty cycle affect the voltage since this is not a dc-dc chopper. Since the circuit has a LC filter, there should be smoothing voltage output but I just get full wave. Am I taking the wrong output?