hannover90

Member level 4

Hello all,

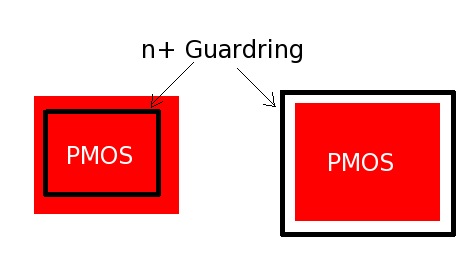

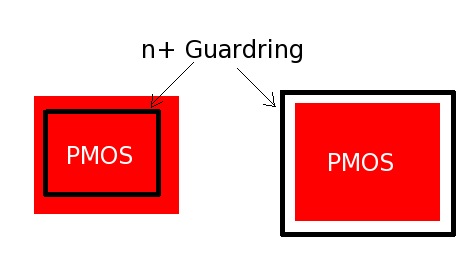

I have a question about guradring arround PMOS:

should be the n+-Guardring inside of NWell or outside?

Thanks for any reply.

I have a question about guradring arround PMOS:

should be the n+-Guardring inside of NWell or outside?

Thanks for any reply.