Barbarawi

Junior Member level 2

- Joined

- Oct 13, 2012

- Messages

- 20

- Helped

- 2

- Reputation

- 4

- Reaction score

- 2

- Trophy points

- 1,283

- Activity points

- 1,468

in the last post ::

press down link . to understand the project !

https://www.edaboard.com/threads/270615/

so far everything in the software "ISIS Proteus " working as I need

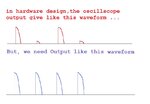

but in the LAB , when I connected the circuit .. the output is not like the output in the ISIS ..

I could not figure out what's the problem !! :shock:

this attachment can at least describe the problem !!

is the problem from the type of the SCR thyristor ?!

but if it's the problem why in the half first cycle there's an output !?

so the problem in the next half cycle of the period

press down link . to understand the project !

https://www.edaboard.com/threads/270615/

so far everything in the software "ISIS Proteus " working as I need

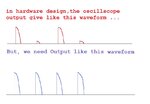

but in the LAB , when I connected the circuit .. the output is not like the output in the ISIS ..

I could not figure out what's the problem !! :shock:

this attachment can at least describe the problem !!

is the problem from the type of the SCR thyristor ?!

but if it's the problem why in the half first cycle there's an output !?

so the problem in the next half cycle of the period