sougata_vlsi13

Member level 4

- Joined

- Apr 19, 2013

- Messages

- 77

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Location

- India

- Activity points

- 1,980

FPGA implementation of LDPC decoder using VHDL

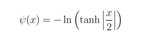

I am implementing LDPC decoder with the use of belief propagation in log domain and platform is VHDL.but in LDPC there are so many exhaustive formulas including matrix calculation,tanh functions and some small small formulas as well.I am not getting how to implement those formulas in VHDL.

I am implementing LDPC decoder with the use of belief propagation in log domain and platform is VHDL.but in LDPC there are so many exhaustive formulas including matrix calculation,tanh functions and some small small formulas as well.I am not getting how to implement those formulas in VHDL.