yefj

Advanced Member level 4

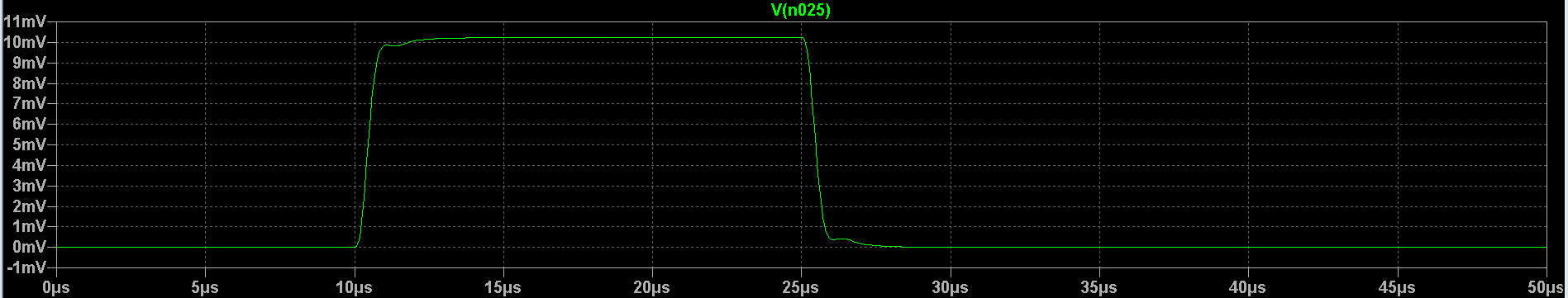

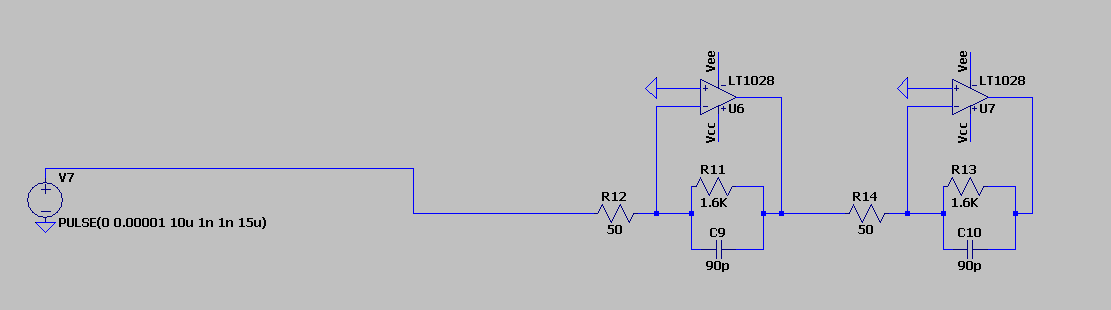

Hello, My simlation shown bellow has no offset voltage problem at all.

However in real life i am afraid that i would get a constant offset to the output instead of zero .

Am i correct?

I tried to plus many resistor in here and i cant see when can i put a potentiomater so in case i would have offset in real life then i would be able to fix it.

where can i connect a potentiometer (resistor in simulation) so could tune the offset ?

Thanks.

However in real life i am afraid that i would get a constant offset to the output instead of zero .

Am i correct?

I tried to plus many resistor in here and i cant see when can i put a potentiomater so in case i would have offset in real life then i would be able to fix it.

where can i connect a potentiometer (resistor in simulation) so could tune the offset ?

Thanks.